1 引言

驱动单元作为大功率模块,其中的放大电路、开关电路和逆变电路等主电路可能对电磁环境存在干扰,为此,在设计驱动模块时,必须考虑电磁兼容性问题,避免驱动单元对外界的干扰。

2 电磁兼容基本原理

电磁兼容性指电器及电子设备在共同的电磁环境中能执行各自功能的共存状态,均能正常工作互不干扰,达到兼容状态[3]。

电磁干扰可以通过时域和频域进行表示,大部分干扰信号都是时变的,为讨论和分析方便,都采用频域分析方法为宜。典型的信号表示方式有正弦、非正弦、周期性、非周期性和脉冲等,它们都是通过空间辐射和通过导线传导的。工程中对非周期信号和脉冲信号运用较多,将干扰信号用f(t)表示,非周期性信号傅立叶积分为

电磁干扰是通过电场和磁场进行传播的,因此,其基本单位也可以用电场和磁场的单位来表示,工程上普遍采用分贝来对电磁干扰进行量测,即db。

3 电磁兼容具体实施

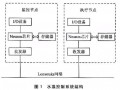

在驱动单元外壳选取时,应综合性价比考虑屏蔽效果较好的材料。在驱动单元的的设计中,中间点钳位型pwm逆变电路作为主工作电路,在功率器件开关时,电路会产生谐波电流,同时高频成分会向空间辐射。pwm逆变工作电路如图1。

为此,在元器件选择、电路板设计和接口设计等各个环节就应充分考虑电磁兼容性,使驱动模块工作在正常状态而不影响其他设备。

3.1 元器件的emc考虑

为达到电磁兼容而使用的元件通常是采用减少并联通路阻抗的方法来减小噪声电压或增加电流通路阻抗来减小噪声电流[1]。

所有元件及互连线都会产生谐振现象,因此在元件选择上,要充分保证线路的低阻抗配电。串联谐振电路的输入阻抗很低,但是根据电路不同的q值,输出电压可能大大高于输入电压,由于大电流高电压的出现,串联谐振非常容易产生高电平的辐射或传到发射;并联谐振会形成一个高的线路阻抗,也会产生高电流。

3.2 电路的板级emc考虑

在电路原理图设计时,就应充分考虑一般元器件和功率器件的放置,主要应该注意以下五点:

(1)控制芯片无用端要通过相应的匹配电阻接电源或接地集成电路上接地或接电源端都要接,不要悬空;

(2)继电器需要匹配上高频电容;

(3)每个集成电路需配一个去耦电容;

(4)降低负载电容,以使靠近输出端的集电极开路驱动器便于上拉,电阻值尽量大;

(5)看门狗电路上不要使用可编程器件。

在pcb设计时,尽量不要使用单面板,同时,模拟电路和数字电路要分开布局;中、高速电路也应分开布局;接地线要明确,不能所有接地都共用;pcb走线上需串接电阻,以降低控制信号线上下沿的跳变速率;处理器或发热器件需通过导热材料与其它芯片隔离,并在处理器周围多点射频接地[2]。

在pwm逆变工作电路上,为限制输入端谐波电流,可以在直流环节前端并联滤波电容器,如图2所示;同时还可以在直流母线上串联直流电抗器。另外,可以在电路的输入端加谐波滤波器,此方法加装简单、成本低、维修方便,但是容易受系统参数的影响。

3.3 接地考虑

接地是电磁兼容重要措施,接地可以降低功率模块噪声、降低串扰和防止静电的积聚。驱动单元的接地原则是信号地和电源地分开;高功率在最近的位置单点接地;同时ac安全地应与单元外壳相连。

3.4 接口滤波考虑

为方便通讯,驱动单元都留有rs232或rs485接口,为此,设计中接口电路需进行滤波处理。通常采用差动线路驱动和接收的方法来提高线路接口的抗扰度。低于信号电平并加在非畸变信号上的噪声脉冲电压与叠加在畸变信号上的噪声脉冲相比,不可能超过接收器输入端的开关阈值,因此在接收器输入端加端接电阻可以减少反射并改善信号质量和提高电路接口抗扰性。差动接收电路如图3。

4 结束语

驱动单元的电磁兼容处理问题是工程人员在设计过程中经常遇到但是必须解决的,文中给出的几种处理方法已在实际运用中得要验证,效果较好。