本文介绍精确测量现代高安全性、高速半导体存储器的辐射灵敏度需要考虑的一些测试方法,及时测试以防止宇宙射线对关键汽车电子系统的损坏。

因为显而易见的安全原因,汽车线控驾驶技术对汽车电子系统的可靠性要求越来越高。与此同时,日益降低的成本的要求在汽车电子子系统中采用商用最新的半导体元器件。

半导体存储器现在是、将来继续是汽车电子子系统的基本器件。随着未来几年中对汽车电子的要求和智能程度的提高,半导体存储器在数量、密度、速度和复杂性上不可避免地要增加。

半导体存储器可靠性的一个方面是其对辐射的灵敏度,人们对此已经进行了透彻研究。

在早期半导体存储器中,封装材料中发现的放射性污染会发射阿尔法粒子(Alpha particle),人们终于发现这就是早期计算机中出现严重系统故障的根本原因。幸运的是,早在微电子在汽车中广泛应用之前,人们已经确定并大部分地解决了这个问题。

然而,1994年IBM的研究发现,存储器中的地电平因宇宙射线引起的中子通量所造成的软错误率(SER)很大,并且SER在较高纬度地区如美国丹佛急剧增加。

从这些数据可以得到结论:宇宙射线引起的半导体存储器故障不再是一个“航天问题”。在汽车电子系统设计中,必须考虑这种故障的发生机制。可靠性工程师必须精确地估计他们在设计中所采用的商用存储器件对辐射的灵敏度。因此,需要测试能力以精确地测量现代存储器件的辐射灵敏度。

测试任务

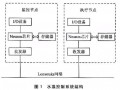

下图显示了经典的同步动态RAM(SDRAM)存储器架构的方块图,其功能包括:

—以额定速度同步内部存储器工作的数字锁相环(DLL);

—为不间隔连续传输数据进行数据交织的多个模块;

—控制内部管道工作的延迟电路;

—从单一外部起始地址产生突发串行或交织地址的逻辑;

—选择阵列中单元的字线和位线编码器;

—刷新电路

—在读周期期间检测数据状态的感应放大器;

任何测试程序都要考虑上述每一个功能的正常工作,以精确估计存储器的辐射灵敏度。

1991年的一项研究显示,随着器件速度的增加,辐射引起的故障率会急剧增加,其中大部分原因是感应放大器的易受攻击性随着频率的增加而增加。

在主动感应过程中,由感应放大器测量的差分电压很小,并且易于受到辐射引起的单次事件的扰乱(SEU)。随着时钟速率的增加,感应放大器易于遭受单次事件效应攻击的时间百分比会增加。此外,由于存储单元的大小和工作电压的减少,感应放大器更易于遭受辐射引起的错误的攻击。

因此,要在存储器以最高可能的数据率运行且以满指标工作时,对存储器测试来获得精确的软错误率(SER)测量值。

多段工作

现代存储器采用多段设计,容许交织数据字以实现高速工作。所测得的SER受到所激活的感应放大器数量的重要影响;也就是说,受到同时工作的存储段的数量的影响。

因此,必须利用并控制不同段的交织方案以量化它们对SER测量的影响。

上图显示了一个激活了所有4个存储段的存储器模式序列的例子,它利用突发和反应时间来生成待以“无间隔”操作输出的连续数据流。这种工作模式因具有高速数据传输的好处而受到某些计算操作的青睐。然而,这种模式也更易于遭受辐射引起的错误的攻击,因为它同时激活了所有段,因此,在最敏感的状态下具有更多同时工作的感应放大器。

在DLL“保持锁定”的速度之上进行测试

为了最小化易受辐射攻击的存储器和系统,工程师必须在各种交织、突发和激活方案下分析存储器的辐射灵敏度,并相应地设计周围的系统工作。

现代存储器利用数字锁相环(DLL)来同步各种内部电路的工作,以实现高速数据传输。DLL在某一个频点不能保持同步。

现代同步存储器的最小“保持锁定”的频率呈现上升的趋势。最小DLL频率指标超过100MHz的情况很常见。在最小频率之下,存储器工作在不同的模式,它不会反映真实系统中存储器的工作。

一些研究在10MHz数据率下测量了存储器的辐射灵敏度,远远小于存储器DLL“保持锁定”的频率。为此,那些测量结果没有反映存储器实际工作的辐射灵敏度。精确的辐射灵敏度测量要求,当存储器以最高可能数据率(至少要高于最小DLL工作速度)运行时,对存储器进行测试。

捕获全器件位图

全阵列位图对于研究存储器的辐射灵敏度是至关重要的。位图错误是识别阵列位置故障关系的主要工具,并利用该信息来优化存储器和系统设计以减少辐射灵敏度。

例如,位图可以回答这样的问题:两个存储器具有不同的布局灵敏度,那么,它们有不同的辐射灵敏度吗?最敏感的位是在子阵列边沿还是在子阵列的中心附近?有没有内部器件对电源分布敏感?

全阵列位图排列和存储必须接近实时,以便连续监测随时间变化的单次事件效应,并容许测试存储器刷新的依赖性。

存储器“扰乱”数据存储的位置,并“感应”写到器件阵列的数据,从而容许更密集地布局数据。两条临近的外部地址频繁地从存储器阵列中的不同物理位置实际读写数据。

在阵列中的临近位通常具有不同的“感觉”。一位代表的“1”作为单元的充电状态;下一位代表的“1”作为单元的未充电状态。这就称为位折叠(bit folding)。

充电单元的辐射灵敏度高于未充电单元的辐射灵敏度,因为,所引起的致电离辐射趋向于给单元放电。因此,如果工程师往阵列中全部写入“1”,那么,阵列的辐射灵敏度就会被低估;反之,写入全“0”也一样。

为了精确测量和比较存储器的辐射灵敏度,测试系统必须解决每一个器件的“扰乱”方法。传统上,从商用存储器制造商不便拿到拓扑扰乱信息。因此,在辐射灵敏度测试期间,汽车电子可靠性工程师必须确保解决拓扑扰乱问题,以建立对精确测量辐射灵敏度的信心。

因为存储器制造商在重要的任务和高安全性的应用(甚至在通用的消费应用)中面临日益增加的辐射引起的故障率,他们越来越愿意在此领域开展合作。

软错误功能中断(SEFI)的测试要求

暴露在辐射下的存储器不仅仅丢失数据。有时侯,如果存储器复杂控制电路(刷新、段控制、突发、模式控制等等)的敏感区域遭受辐射的袭击,存储器就会停止工作。这些事件就是软错误功能中断(SEFI)。

SEFI测试挑战包括上述所有SEU测试要求,以及下列独特的要求:

—要快速识别间歇的SEFI事件并分流到测试子程序;

—要快速识别SEFI的根本原因;

—要快速识别最佳的SEFI恢复程序;

如果测试数据率和位图捕获足够快的话,所有这些要求都可以满足。

非易失性存储器辐射灵敏度测试面临的挑战

对于分析辐射灵敏度的研究人员来说,非易失性存储器(NVM)具有独特的测试挑战。现代NVM器件具有高速、同步控制电路和I/O操作,展现了与上述高速SDRAM一样的挑战之外,NVM器件的测试要依赖对存储阵列中每一个单元的模拟电压门限(Vth)的测量。下图显示了Vth对闪存器件的典型影响。

对16Gb(及以上)容量NVM器件的电压门限的测量要耗费很长时间。电压门限的分布随辐射暴露时间而改变。对所有单元的实际Vth分布的测量需用在多个引脚上进行非常高速的电压测量。专用电压门限测量电路和方法可以把Vth测量时间从几天减少到几分钟。

实时位图捕获容许在大容量NVM器件中测量辐射引起的错误的时间历史。

本文小结

现代存储器对辐射引起的错误展示了重要和日益增长的灵敏度。对现代半导体存储器的辐射灵敏度的精确测量和比较,需要控制与器件复杂性相当的测试条件。