摘 要:介绍应用CPLD控制OV7110图像传感器进行高速数据采集,提供了一种利用PC机外设对图像读取的解决方案。按照该方法制作的系统,经过实验验证效果良好。

关键词:CPLD;CMOS图像传感器;高速采集系统;OV7110

在当前图像传感器市场,CMOS传感器以其低廉的价格得到越来越多消费者的青睐。在目前的应用中,多数采用软件进行数据的读取,但是这样无疑会浪费指令周期,并且对于高速器件,采用软件读取在程序设计上、在时间配合上有一定的难度。因此,为了采集数据量大的图像信号,本文设计一个以CPLD为核心的图像采集系统,实现了对OV7110CMOS图像传感器的高速读取,其读取速率可达8 Mb/s。

1、硬件电路方案

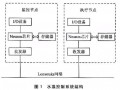

图1为基于CPLD的OV7110CMOS图像传感器的高速数据采集系统原理框图,他主要由2个部分组成:OV7110的参数设置电路和图像采样电路。

1.1 OV7110的参数设置电路

系统在上电后需要对CMOS采样芯片进行初始化,以 确定其工作模式、窗口大小、扫描方式、输出数据格式等。这些参数是通过OV7110芯片上的SCCB接口进行的。

SCCB是OmnVision公司开发的一种双向三线的同步串行总线,引线接口有使能线SCCB_E,时钟线SIO_C,数据线SIO_D。其中SCCB_E低电平有效,如果将其接地,那么SIO_C,SIO_D的工作方式十分类似于I2C总线。OV7110工作模式、窗口大小、扫描方式、输出数据格式均可以通过相应的寄存器来设置,本系统把AT89C51作为主设备(MasterDevice),OV7110作为从设备(Slave Device),采用AT89C51的P1.2和P1.3口用软件模拟SCCB总线,把其参数写入其内部对应的寄存器。与I2C总线一样,在SCCB总线中主设备发送一个字节后,从设备需要将数据线SIO_D拉低作为应答信号(ACK)返回给主设备,才能表示发送成功。值得注意的是由于CMOS器件所能承受的灌电流很低,所以接至时钟线SIO_C、数据线SIO_D的上拉电阻阻值应在3~5 kΩ之间,并且对于主设备AT89C51发送参数完毕后,需立即释放数据线SIO_D以保证其处于悬空状态,即AT89C51在送完一个字节后立即执行一条指令,使数据线SIO_D发出读取信号的操作。

1.2 图像采样电路

本系统设置的工作模式为黑白,分辨率取到了最大640×480。CMOS芯片的数据输出波形如图2所示(为了便于分析,该图只是示意图)。图中VSYNC为垂直场同步信号,其下降沿表示一帧图像的开始。HSYNC为水平行同步信号,其上升沿表示一行信号开始。HREF为水平窗素时钟信号,即数据输出同步时钟信号,其下降沿更新数据,上升沿数据是稳定时期,可以读取数据,其数据按行输出。Y为图像灰度数据。

下面介绍CPLD如何控制CMOS芯片的数据读取。

首先按顺序检测VSYNC和CHSYNC信号是否有效,应该注意的是要防止毛刺信号干扰。由于毛刺信号时间很短,故在本设计中采用了设标志位的方法,即当检测信号有效沿后(对于VSYNC是上升沿,而对于CHSYNC是下降沿),在等待一定时间后再次检测信号,看其是否仍然有效,如果有效,则说明信号是正确的。其源程序如下:

由于象素数据按照PCLK时钟输出,所以用来存储图像的RAM的使能信号RCE和写信号RWE、读信号RRE以及地址信号ADDRESS都是由CPLD用他来产生。其中,读信号RRE在CPLD写操作中置“1”即可。由于在数据输出时,PCLK上升沿信号稳定,而RAM是在WR上升沿将数据写入,因此可以在HREF有效后(HREF=1)采用PCLK作为写信号RWE。同时设计一个二进制计数器,在HREF有效后,以PCLK的下降沿为触发沿对PCLK做计数,并取其输出作为RAM的地址信号ADDRESS。这样在PCLK的下降沿更新地址信号,接着在上升沿存贮数据。源程序如下:

设置往RAM写信号RWE

由于图像象素点个数已知,即数据个数已知,故在计数完毕后CPLD发出计数完毕信号R,同时把指向RAM地址线ADDRESS和读写信号RWE、RRE切换连至AT89C51的地址线和读写信号WR、RD。AT89C51接受到中止信号R后开始读取RAM中的数据,并通过RS232串口上传至PC机。需要注意的是RAM地址达到512 k,而单片机最大寻址空间只有64 k,所以在读取RAM时采用分页读取,每次读64 k,即从P1口中抽取3根线作为RAM的最高的三位地址和P0和P2口共同组成AT89C51的地址线。

2、结语

采用CPLD对CMOS图像传感器进行数据采集的方法,可以把CMOS的主动器件通过CPLD变为可控制的方式,实现了对CMOS图像传感器的高速数据读取,按照该方法制作的系统,经过实验验证效果良好。这种信号读取的方法还可以在其他诸多需要高速图像数据采集的场合应用。