关键词: ARM MPEG-1嵌入式系统 数字视频

引言

随着计算机技术、多媒体和数据通信技术的迅速发展,数字视频的应用越来越广,如视频监控、视频会议和移动电视等。数字视频数据量巨大,不利于传输和存储,使其应用受到很大限制。为解决视频数据的存储和传输问题,唯一的途径就是对视频数据进行压缩。常见的视频压缩方法有MPEG系列和H.26x系列。考虑到压缩技术的成熟度、成本和主要用途,采用MPEG-1作为压缩标准,设计出基于ARM处理器的嵌入式数字视频记录系统。该系统适用于视频监控、视频会议等多种应用场合,同时还可安装在飞行器上,用于实时记录飞行器的飞行及训练过程中的各种信息。

目前,市场上有大量的基于PCI总线的MPEG-1视频压缩卡和PC机构架的网络视频服务器。与之相比,我们设计的视频记录系统具有成本低、体积小和功耗低等优势。

1 系统工作原理

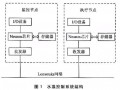

视频压缩记录系统的设计着眼于控制器的嵌入化和整体的便携性。本系统主要由3部分组成,即压缩部分、控制部分和存储部分。视频记录系统的结构组成如图1所示。其中压缩部分由MPEG1音视频压缩电路组成,主要功能是实现对输入的音视频信号解码、数字化和压缩编码,产生MPEG1程序流和传输流;控制部分由ARM最小系统组成,用于实现对整个系统的控制、数据流管理和IDE接口控制;存储部分由大容量硬盘或CF存储卡组成,实现对压缩数据的实时长时间记录。

系统启动时,ARM处理器对整个压缩系统进行初始化,首先通过HOST接口对SZ1510内部寄存器进行配置,并使用SZ1510的串行接口模拟I2C总线对视频解码器SAA7113H进行初始化。当设置好MPEG-1的压缩格式及数据速率后,系统开始正常工作,音视频信号经AK4550音频处理芯片和SAA7113视频处理芯片进行A/D转换,输出8位的PCM格式数字音频信号和4∶2∶0的YCbCr数字视频信号,传入SZ1510音视频压缩采集芯片进行处理,将数字音视频数据转化为符合MPEG-1格式的混合影视文件,最后MPEG1数据流在ARM处理器的控制下通过IDE接口写入硬盘或CF卡。在工作时,ARM还将不断监视相关信号,并在图像中加入相应的标志,直到接收到关机信号,系统自动结束压缩工作。

2 硬件电路设计

由于MPEG-1压缩算法需要很大的运算量,用软件实时完成比较困难,所以在本系统中主要依靠专用芯片实现对视频信号的高效压缩。目前,常用的MPEG-1压缩芯片有VW2010、W99200F、WIS 7007SB等。本设计采用的是Zapex公司的SZ1510 MPEG-1 A/V编码芯片,自身完成音视频的同步编码,16位HOST接口易于与多种微处理器连接。另外,该芯片还可以直接控制视频解码芯片SAA7113H、音频解码芯片AK4550VT和SDRAM(KM416S1020CT-G10)。CPU采用Philips公司的ARM7TDMIS内核微控制器LPC2214,通过其I/O端口控制IDE接口硬盘或CF卡的数据读取和存储。

2.1 MPEG-1压缩电路设计

SZ1510是一个 MPEG-1和运动JPEG图像编码器。其内置的视频压缩核经过优化,适合高效、实时的MPEG1数字图像压缩,具有功能多、功耗低、温度范围宽等特点;同时整合了TI公司的TMS320C54X高性能DSP内核,可依据MPEG-1标准对音视频同步编码。

(1) 时钟同步电路设置

SZ1510是一个复杂的视频压缩小系统,要完成音视频的同步,MPEG-1视频的压缩以及系统内部数据流的复合、调度;时钟关系较为复杂,是系统设计的一个难点。时钟配置可分为主时钟、音视频时钟、视频压缩核时钟、DSP核时钟以及扩展的I2S接口时钟几部分。其功能和关系为:

◆ 主时钟。SZ1510的主时钟为稳定的27 MHz(CLK)。该时钟在芯片内部被PLL1倍频为81 MHz,驱动SZ1510的视频压缩核及SDRAM。PLL2连到DSP内核,通过软件配置使其工作在94.5 MHz,用于音频压缩和系统数据流复合。

◆ 音视频时钟。视频时钟来自视频解码器,典型值为27 MHz。音频时钟由视频时钟分频产生。

◆ I2S接口时钟。本系统中在音视频同步设计中使用I2S接口的从模式,由SZ1510产生串行时钟和帧同步信号。

(2) 主机(HOST)端口设置

SZ1510作为从设备,受主机控制,其HOST接口是SZ1510的控制和数据交换接口。SZ1510可以选择复用或不复用的Intel和Motorola总线类型;不复用总线,又可以分为8位和16位。具体的主机端口由HCONFIG[1∶0]引脚和SysConfig[3]寄存器配置。在本系统设计中,通过跳线把HCONFIG0拉低,HCONFIG1拉高,使其工作在Intel 8051类型的非复用的16位数据总线模式下。

2.2 LPC2214微处理器电路设计

LPC2214是一款基于32位ARM7TDMI-S,支持实时仿真和跟踪的CPU;带有16 KB片内SRAM、256 KB嵌入的高速Flash存储器、128位宽度的存储器接口和独特的加速结构,使32位代码能够在最大时钟速率60 MHz下运行。芯片内部集成了多种串行接口。LPC2214与SZ1510的接口和控制关系如图2所示。在设计中,需要注意的是保持SZ1510读写时序与内部时钟的同步。通过CS3选通SZ1510实现控制字和数据的交换。

2.3 IDE接口设计

由于LPC2214芯片不具备IDE接口,因此在本系统中使用通用I/O 口,模拟产生ATA 设备的读写时序,实现对IDE硬盘的可靠读写操作。图3为LPC2214与IDE硬盘连接图。其中,P2.16~P2.31作为数据线,P1.16~P1.20作为地址和选通信号,P0.17和P0.20为设备的复位和状态请求信号,用P0.21和P0.19实现读写控制。

3 系统软件设计

系统软件由主程序和若干个子程序组成,工作流程如图4所示。主要的子模块有:SZ1510 的设置与控制、IDE接口驱动和文件系统的管理。

3.1 SZ1510的设置与控制

SZ1510共有128个寄存器,每个寄存器都有一个索引号。当SZ1510工作在非复用总线模式下时,外界对寄存器的访问都是通过IOAR和IODR来完成的。访问时首先将这个寄存器的索引号写入IOAR,然后将要写的数据写入IODR。

SZ1510设置与控制过程如下:

① 向中断使能寄存器写入0x40,以使能Ready中断;

② 等待SZ1510的Ready中断;

③ 等到Ready中断后,向SZ1510的0x1E寄存器写入0x0A,设置它内部的DSP时钟为94.5 MHz;

④ 向0x013寄存器写入0x55,对SZ1510进行软复位;

⑤ 向中断使能寄存器0x0C写入0x40,以使能Ready中断;

⑥ 等候RDY中断;

⑦ 待Ready中断后对SAA7113进行初始化;

⑧ 对SZ1510进行软复位,即向0x0B寄存器写入0x55,同时向0x0C寄存器写入0x40;

⑨ 等待Ready中断,等到后向SZ1510的内部DSP装载二进制代码;

⑩ 进行SZ1510内部视频压缩核的二进制代码装载,具体装载步骤如下:

◆ 向0x08寄存器写0x04,发送开始命令;

◆ 等待Ready中断,清除Ready中断;

◆ 向Data in寄存器0x01写256个字节;

◆ 等待End of Data中断,然后清除中断;

◆ 查程序空间的代码是否装载完毕,如没有,则继续装载。

3.2 IDE接口驱动

本系统采用LPC2214的通用可编程I/O口模拟ATA设备的读写时序,实现对硬盘的读写。这里给出模拟写ATA 设备寄存器的步骤(读ATA设备寄存器的步骤类似):

① 关系统中断,预防在写寄存器操作中产生中断;

② 设置GPIO 模拟ATA 接口数据的引脚为输出状态,准备输出数据到设备数据线;

③ 设置ATA 设备寄存器的相应地址;

④ 设置GPIO 模拟ATA 接口数据的引脚电平为要写到设备的值;

⑤ 使写ATA 设备寄存器信号为低电平;

⑥ 使写ATA 设备寄存器信号为高电平;

⑦ 取消ATA 设备寄存器地址的选择;

⑧ 设置GPIO 模拟ATA 接口的数据总线引脚为输入状态,释放总线;

⑨ 开系统中断。

3.3 文件系统管理

本设计中采用的是面向嵌入式系统的小型文件系统ZLG/FS [1],主要用于将数据存储为标准的文件格式和对整个文件系统的管理。同时,为了便于音视频的检索和查询,以及防止非法断电造成大量未保存数据的丢失,在系统中设置了每间隔一定的时间(30 min)将压缩数据存储在以系统时间命名的新文件里。

4 结论

经测试,系统可实时长时间记录外部的音视频信号,记录的压缩数据流符合MPEG-1图像压缩国际标准。在设计中,采用的压缩视频流速率为1.5 Mbps,1小时的视频数据量为(1.5 Mbps/8)×3 600=675 MB,对于一个40 GB的硬盘,系统连续记录时间接近60小时。系统体积小、功耗低,便于移动环境下对音视频数据的实时长时间压缩记录。