摘要:利用VHDL硬件描述语言在FPGA中设计直流伺服电机控制器.其含4路PWM控制器,每个控制嚣均分配一个lD。当地址线Addrcss选中某个ID时,表明对谊PWM控制器操作.利用ALE、WR信号将地址线信号锁存.电机缡码器捕获单元则获得电机码盘信号,再通过总线控制器送给MPU读取.由此判断电机转动速度。

关键词:FPGA;硬件描述语言;直流伺服电机控制器

引言

直流伺服电机处理器.如单片机,DSP具有产生PWM信号和捕获电机编码器信号的能力,但对IC产生PWM信号的通道数目和电机编码器捕获通道数目有限。对多个直流电机的伺服控制很难满足要求。故设计基于FPGA直流伺服电机控制器。

1、控制器构成

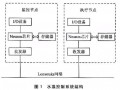

在Cyclone EP2C5T FPGA内部设计各4路PWM发生器和编码器脉冲捕获单元。其PWM信号通道和编码器脉冲捕获单元数目可基于VHDL硬件描述语言按需调整。如图1。包括总线和4路PWM控制器、4路脉冲捕获单元、分频器l,分频器2。总线控制器根据WR、RD、ALE信号完成FPGA内部地址锁存及8位OUTPUT总线.8位INPUT总线的控制。FPGA外接20 MHz有源晶振,时钟信号经分频器1分频后得到20kHz占空比为50%的方波信号.4路PWM控制器以该信号为基准,产生频率为20kHz,占空比可调的4路PWM信号.4路PWM信号可依4位地址线独立控制。4路脉冲捕获单元用于对电机编码器脉冲信号进行捕获.通过总线控制器将脉冲捕获值读出到8位I/O口上。

分频器2将20 kHz方波信号20000分频得到IHz占空比为50%的方波信号,直接驱动LED灯,指示系统状态.EP2C5FPGA内部逻辑在Qoartusll。6.0环境下使用VHDL硬件描述语言实现。

2、VHDL设计伺服电机控制器

2.1总线控制器设计

写入伺服电机控制器是PWM调节值,读出的是电机编码器数值.因此.需设计总线控制器完成上述过程.基于FPGA的直流伺服电机控制器为外部处理器(如单片机等)提供总线接口。类似8051的MCU地址线、数据线复用的特点设计了总线控制器.控制总线包括WR、RD、ALE;数据/地址总线为8位I/O。

总线控制器逻辑电路如图2,使用2片74244实现。WR、RD信号使输入/输出总线交替进入高阻态,实现伺服电机控制器数据的写入或读出。

2.2 PWM控制器设计

PWM控制器的VHDL硬件描述语言如下:

因设计中有4路PWM控制器,为每个控制器分配一个ID。上面程序中setAddress为该PWM控制器的ID,当地址线Address选中该ID时,表明对该PWM控制器操作.利用ALE、WR信号将地址线信号锁存。每个clk信号上升沿到来时将count加l处理。比较count与databus的值,实现PWM信号占空比的调整。并可根据需要在FPGA资源允许前提下,任意增加PWM控制器。

2.3电机编码器捕获单元设计

电机编码器捕获单元获得电机码盘信号后,通过总线控制器送给MPU读取,来判断电机的转动速度。VHDL硬件描述语言的程序源码如下:

多个编码器用setAddressL、setAddressH定义每个编码器的地址。当Address与setAddressL、setAddressH相同时选中该编码器捕获单元.同时用RD、ALE控制将捕获的数据传到总线上。

2.4分频器l设计

FPGAEP2C5T全局时钟信号外接20MHz有源品振,为得到20kHz的PWM信号,在EP2C5T内用VHDL设计了分频器.VHDL程序如下:

分频器2的原理与分频器1相同.将20 kHz方波信号20000分频得到l Hz的方波信号。

3、结语

利用VHDL硬件描述语言在FPGA中设计的直流伺服电机控制器,可满足对多路直流电机的伺服控制。该控制器在4路直流伺服电机控制系统中可稳定可靠的运行。