关键词:PC104;程序控制;可编程逻辑器件(CPLD);电磁选针

1 引 言

提花系统已在我国纺织行业广泛应用,但传统的提花系统大都采用单片机做控制单元,然而由于单片机本身结构与功能的限制,使系统的数据处理速度慢、抗干扰能力差,并且系统的各种工作状态及操作状态往往仅通过数码管或发光二极管来显示,显示结果不直观,这样给操作工人带来很大的不便。为了改善系统性能,提高织花效率,我们设计了该控制系统。本设计采用PC104工控机作为控制单元,提高了整个系统的抗干扰能力,且数据处理速度比原来提高了数倍,同时采用C语言编程,各种信息状态在液晶屏上直接通过汉字显示,具有良好的人机对话功能。

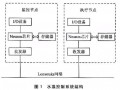

2 系统方案及结构

该系统主要由3部分构成:PC104转接卡、电磁选针接口、软件设计及编程。PC104转接卡主要将工控机发送的织机控制信息进行驱动、转换并发送给电磁选针接口,同时接收外界各种控制命令,如:停机、倒车、找纬等[1]。电磁选针接口将提花控制信息发送到织 针电路,并读取校验状态、机械OE信号等。软件程序功能:分析提花织物花型信息并转换为织机控制信息,分析总线所读取的各个状态并实现人机对话。

2.1 PC104转接卡的设计

转接卡单元以并口扩展芯片8255A为核心,主要构成部分有:译码电路、驱动电路、并口扩展、输入输出接口等。

译码电路主要利用GAL16V8芯片的编程,对地址总线进行逻辑组合确定8255A的地址(0x208~0x20b)。8255A的3个扩展口功能的定义如下:PA口定义为基本输入口,用来读入外界的人工控制信号。PB口占用PB0为OE信号的输入、PB1为校验输入端、PB2为机械维修信号。PC口定义为基本输出口,PC4为时钟端、PC5为数据信号、PC6为STB信号、PC7为停止信号[2]。

2.2 电磁选针接口设计与结构

电磁选针接口采用CPLD器件ATF1508AS将接口中所有的信号连接起来使硬件的调试软件化,对电路时序及组合逻辑的修改极其方便。器件内部的时序和逻辑关系均用AHDL语言编程来实现[3,4]。ATF1508AS的内部设计可分为4个模块:自动检修电路、选针信号停机状态进行检修时,ATF1508AS将系统时钟分频得到内部OE和时钟信号提供给织针电路,通过内部时钟将维修数据发送到织针电路来对其进行检测和维修。

正常工作时,ATF1508AS将转接卡发送端的数据、时钟、STB提花信号输出至织针电路。OE合成模块将正向的机械OE1、反向机械OE2、织针位置OE3按照织造工艺合成为最终有效的OE传送给转接卡。

校验判断模块通过将织针电路返回的数据及校验位进行逻辑判断,来置转接卡的校验状态,以判断是否重新发送数据或故障提示。

电路原理如图2所示,其中DB25插孔作为转接卡接口和电磁选针接口的信息交换通道来传递各种信息——提花数据、时钟、STB、停止信号等。ATF1508AS通过读拨码开关S1的状态来确定是将内部OE、数据 和时钟信号提供给织针电路来对其进行检测和维修,还是将转接卡发送端的提花信号输出至织针电路进行提花织造。若是进行提花织造则按照织造工艺将正向的机械OE1、反向机械OE2、织针位置OE3进行逻辑合成,向转接卡提供有效OE。

3 软件设计及流程

提花数据发送时序如图3所示。

由时序图可看出在OE无效区(5/6 OE),程序可发出时钟信号并在对应的数据位输出提花信息。若校验无误,则置STB位,将数据输出至织针电路,等待OE有效进行提花织造。若校验结果为数据传输错误则再次发送数据,再次进行校验。若数据传输连续3次错误则停机并提示数据传输故障。

每梭数据必须在OE无效区内正确发送到位,否则织造将出现漏织或跳织,故OE的周期及梭针的个数直接决定了数据时钟的最长周期,但为了提高系统的抗干扰能力及考虑数据的传输故障的二次发送,时钟周期又不能一味的缩短。故时钟周期T的计算公式为:

T≤(5/6Toe)/3N

其中:Toe为OE的周期(机械转数),N为每梭的织针数。提花数据发送流程如图4所示。

本设计中数据时钟的周期采用自适应控制方法,根据每梭数据的多少(N)自动选取延时系数来确定时钟周期,从而达到系统既能在OE无效区内正确发送完数据,又能达到抗干扰的最优化。

4 结 语

经过现场测试表明该系统对于672针的龙头,织速可达500梭/min。对于1 760针的龙头,织速可达330梭/min,具有相当高的生产效率和稳定性。具有友好的人机界面,操作方便直观。同时软件的自适应设计使本系统可应用于不同针数的龙头,也使系统的抗干扰能力大大提高,在国内具有领先地位。

参考文献

[1] 福瑞,陆培,王春燕,等.单片微机测控系统设计大全[M].北京:北京航空航天大学出版社,1999.

[2] 周明德.微型计算机系统原理及应用[M].北京:清华大学出版社,1999.

[3] 王金明,杨吉斌.数字系统设计与Verilog HDL[M].北京:电子工业出版社,2002.

[4] 廖裕评,陆瑞强.CPLD数字电路设计[M].北京:清华大学出版社,2002.