ZHANG Xiao-yu, ZHAO Long-zhang, FANG Zhi

(Collage of Automation, NanJing University of Industry, Nanjing 210009, Jiangsu province, China)

张晓煜,赵龙章,方 志

(南京工业大学自动化学院,江苏省 南京市 210009)

ABSTRACT: Merging unit is an important part of the secondary protects equipment and electronic transducer interface which defined in the IEC60044. This paper has raised a plan of design merging unit based on ARM9 chips and IEC61850, discussed and analysis the possibility of using a single process chip and introduce a real-time and multitask operation system : Windows CE ,as the operation system of merging unit. We also divide the work of the merging unit, analysis how to realize the multi-thread and multi-priority programming on Windows CE. At the end, we discuessd the advantage of using Windows CE and advanced some prospect of the application of integrate Windows CE and IEC61850.

Key word: ARM; Windows CE; real-time; multitask; embedded system; merging unit; IEC61850

摘要:合并单元是IEC60044中定义的用于电子式互感器和二次保护控制设备接口的重要组成部分,本文提出一种基于ARM芯片和Windows CE的合并单元的设计方案,就采用单一芯片在处理能力上的可行性进行了理论分析,并引入了支持实时多任务的Windows CE嵌入式操作系统作为平台,对合并单元所要完成的任务进行了分工,分析了如何通过编程实现不同优先级多线程分工处理方法。并与使用FPGA+DSP的合并单元进行对比,最后对于Windows CE和IEC 61850相结合在电力系统中的应用和合并单元的功能扩展提出了一些展望。

关键词:ARM;Windows CE;实时多任务;嵌入式;合并单元;IEC61850

1、引言

随着电子互感器技术的发展和成熟,以及近年来一些采用新的设计方法的电子互感器的出现和趋于实用化,我国在变电站的设计和建设中也逐步开始数字化。为了解决数字化变电站设备中存在的不同厂家使用的网络和通信协议互不兼容,通信协议转换繁琐,可靠性低以及维护成本高的问题,国际电工委员会颁布了IEC60044-7/8和IEC61850-9-1等协议标准,并在IEC60044中首次提出了作为接口的重要组成部分“合并单元”的概念。

目前在合并单元中使用比较广泛的是FPGA+DSP的结构,因为FPGA具有独特的FIFO(先进先出)结构,方便于多路采样数据的排序和预处理。数据流经基于FPGA的数据还原模块完成高速数据的接收还原后, 送入DSP中完成一系列复杂协议的处理和滤波。随着目前嵌入式技术的发展,基于ARM架构的处理器应用更加广泛技术也日趋成熟,ARM处理器的多流水线设计、更高的主频和更多的功能所带来的优势也越来越明显。为了满足电力系统对系统稳定性和实时性的高要求以及IEC61850规约对数字化变电站中智能设备的网络化要求,本文引入了Windows CE作为嵌入式合并单元的操作系统。

本文所提出的基于ARM9芯片和Windows CE的嵌入式合并单元的设计方法,利用了ARM芯片速度快,处理能力强、接口丰富、网络功能强大以及Windows CE的实时多任务处理能力强的优点。考虑到IEC61850规约中提出的变电站配置语言(Substation Configuration Language)遵循于XML语法规定,而WinCE完全支持W3C的XML的最新规范,并且微软在.NET Compact Framework 2.0中也提供了功能强大的XML类库,使得操作系统对使用XML格式的数据流处理更加方便和快捷。

2、合并单元的定义及功能划分

在IEC60044-7/8规约中第一次提出了新的物理单元“合并单元”的概念,主要是用来针对使用数字化输出的电子式互感器而设计的,通常是合并单元将一次侧传过来的信号(12路),经过一定的预处理后按照IEC61850规约中所规定的编码格式和协议发送给二次保护、控制设备。由于变电站的数字化是需要逐步实现的,所以在初期的数字化变电站的合并单元设计中不但包含有数字信号接口还有模拟信号接口。

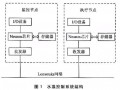

图(1)合并单元的定义

合并单元与电子式互感器的数字输出接口通信具有以下几个重要特点:

(1)同时处理的任务多。

(2)高可靠性和强实时性。

(3)通信信息流量大。

(4)通信速度较高 [2]。

按照合并单元中的数据处理流程可以划分为4个处理步骤:

(1)向高压侧互感器发送同步采样信号并实时接收从采集系统传送的采样数据,对其进行相应处理,使之成为可以被系统所接受和识别的数字信号;

(2)将有用的数据从转换后得到的数据包中提取出来;

图(2)合并单元数据处理流程

(3)对数据进行处理,包括数字滤波,移相,再次打包等操作;

(4)将数据通过以太网发送给二次设备。

同时合并单元还需要解决数据同步的问题。在数字化变电站中,同时有数个合并单元在工作,必须保证不同的合并单元所采集到的数据是在同一时间点上采样获得的,以避免相位和幅值产生误差。目前比较常用的同步方式是由变电站的GPS模块或高精度时钟给每一个合并单元发送同步的秒脉冲信号(同步信号1),合并单元内部在对秒脉冲分频获得所需的时钟信号(同步信号2),并将时钟信号每秒和GPS提供的秒脉冲同步一次,以保证彼此之间采样的同步。

3.合并单元的设计

3.1可行性讨论

首先在硬件方面本文主要使用一片的ARM9芯片来实现合并单元所有控制和数据处理的功能。ARM微处理器是一种高性能、低功耗的32位微处器,它被广泛应用于嵌入式系统中。ARM9代表了ARM公司主流的处理器,具有高主频和5条流水线的设计,已经在手持电话、机顶盒、数码像机、GPS、个人数字助理以及因特网设备等方面有了广泛的应用。

在合并单元工作过程中需要控制传感器对电网中电流和电压的波形进行采样,按照每周波采样80个点计算,每个采样点之间间隔250µs,主频200Mhz的Samsung2410处理器时钟周期5ns,由于采用多流水线设计,平均每个时钟周期可以执行1.1条指令,即每两次采样之间可以执行55000条32位指令,足够处理采样、输入、校检、滤波、打包和输出以及操作系统所需要的一些操作。如果采用主频400Mhz的2440处理器,系统的处理能力将会提高一倍,从而可以把更多的CPU时间放在处理协议、服务和用户接口方面,带来更好的性能和可靠性。

其次,在软件方面引入了Windows CE作为合并单元的操作系统,Windows CE不同于Linux,是严格的硬实时多任务操作系统,拥有256个等级的线程优先权,支持套叠的中断,以及Bounded interrupt response latency(有限的中断响应)等功能,它强大的中断和线程调度机制和内核操作系统服务能够满足不同设备对于时间关键性任务的时间和性能要求。根据测试,在一个主频为200MHz的参考系统中,Windows CE的实时性最小可以达到40~60µs[12]。由于在本文的设计中使用了主频高达400MHz的CPU,系统的实时性理论上可以比测试中提高近一倍,达到或接近20~30µs,足以满足电力系统应用中的苛刻要求。Windows CE的多任务功能使系统可以同时处理数据采样、数据处理、时钟同步、数据发送以及触控屏显示和响应用户输入等任务,线程的优先级越高,其相应速度就越快。

3.2 硬件结构

在变电站的数字化过程中因为种种原因的限制,不可能一步做到所有的电流电压互感器都实现电子化和数字化,会在较长的一段时间内存在电子互感器和常规互感器并存的现象,所以合并单元的输入端会存在数字信号和模拟信号两种输入方式。因此,合并单元还应该保留A/D转换的功能。由于ARM9芯片自带的A/D转换功能的精度较低,需要使用外加的A/D芯片,A/D模块和O/E模块可以直接挂接在系统总线上,CPU可以对其直接寻址,并及时将采样数据读取至内存缓冲区。

图(3)合并单元硬件框图

合并单元发出同步采样信号后,A/D单元和O/E单元同时进行数据处理,A/D单元负责将常规互感器采样信号转换为计算机能够识别的数字信号;O/E单元负责接受电子互感器送来的数字信号,并对其解包,分离出有效信息。由于二者共享系统总线,同时读取12路数据必然会引起冲突,在设计中采用在规定的采样上限时间内按照12路数据的处理顺序依次读入数据。

虽然Samsung s3c2440和Windows CE都可以对触摸屏提供良好的支持,但是考虑到目前合并单元的应用中暂不需要人机交流,而且使用触摸屏会占用部分系统内存带宽和资源,为了保证系统的稳健性,在设计中并没有引入触摸屏。

3.3 软件平台设计

在本文中引入Windows CE作为合并单元的操作系统,Windows CE是一个开放的、可裁剪的、32位实时嵌入式窗口操作系统。它被设计成一种高度模块化的操作系统,以适应不同类型和要求的智能设备,设计者可以根据设备的性质只选择那些必要的模块或模块中的组件来定制属于自己的嵌入式实时操作系统。

Windows CE被分成一些不同的模块,其中内核(Kernel)、图形窗口事件子系统(GWES)、文件系统(Filesys)、和通信(Communication)模块是4个主要模块。一个最小的Windows CE系统至少由内核和文件系统模块组成[10]。在合并单元上应用的系统由于不需要触摸屏人机交互界面,所以GWES模块在定制时可以不选或者是使用带命令行的SHELL。

在合并单元工作的过程中,有些任务是同时运行的不能互相等待的,例如在收到同步信号的时刻,系统可能正在处理数据或正在等待采样值等。为了解决这样的问题,必须使用多个线程来同时执行多个任务。Windows CE支持256个等级的线程优先级,一个线程就是一个可执行单元,当操作系统创建一个进程的时候,同时也会至少创建一个线程,使用线程可以尽可能有效的利用CPU时间。一个进程可以包括多个线程,每个线程都共享包括进程地址空间在内所有资源[10]。按照合并单元所要完成的任务可以划分为如下4个线程:同步、采样、数据处理和发送。这4个线程中同步线程可以被同步信号1唤醒并拥有最高的优先级,其他3个线程的优先级低于同步线程,并都由事件唤醒。

<1>同步线程

理想情况下,合并单元每秒接收一个变电站由GPS或高精度时钟提供的同步信号1,然后按照每周波采样要求分频产生同步信号2,不同合并单元发送的采样信号应是等间隔的,但由于晶振时钟误差的存在,信号2是无法做到完全等间隔的,尤其随着时间的推移,不同合并单元发送的信号2相互之间的误差将累积增大,这是差动保护所不允许的,引人信号1的真正意义也正在于此:多个合并单元每隔1秒被强行同步一次。在1秒内,使用高精度高稳定度的晶振,不同合并单元发送信号2的误差很小。不同合并单元在发送第1个同步信号2时应保证足够的同步精度,其发送时刻应与信号1脉冲的上升沿尽量接近,因为这是不同合并单元所能共同遵循的惟一基准。以后信号2通过各自合并单元的晶振进行等间隔计数发送[13]。同步线程负责接收变电站提供的同步信号1,并对其进行分频产生同步信号2,为了保证不同合并单元之间产生的同步信号2有足够的同步精度,同步线程必须具有进程内最高的优先级,在收到同步信号1以后就可以立刻抢过系统的控制权,分频产生同步信号2,这样获得的同步信号2的发送时刻可以和同步信号1的上升沿尽量的接近。同步线程发送完成同步信号2以后将唤醒采样线程进行数据采集工作。

图(4)多线程编程流程图

<2>采样线程

采样线程被同步线程唤醒后将设定的时间内检查A/D模块和O/E模块的是否送来已经采样/转换完成的中断信号,如果有则按顺序将采样数据读入内存并按照顺序排列,然后唤醒数据处理线程并将数据缓存区地址指针传递过去。如果出现部分通道在规定时限内未送来采样数据,则全部以0填充并设立错误标志。

<3>数据处理线程

数据处理模块主要负责对接收的数据信号进行相关的数字滤波设计, 在合并单元中加入数字滤波器是为了消除 A / D 转换器带来的噪声以及干扰的高频分量。然后, 对数据进行均方根值、相角的有关计算。由于输出的数字量和真实的电流值之间存在相位和幅值误差, 有效频段内的幅值误差在设计滤波器和确定变比系数等参数时能够考虑到, 所以相位误差相对幅值误差而言影响较大, 因此必须对信号进行相位补偿数据处理[1,14]。数据处理完以后存入内存。然后唤醒发送线程并将数据区指针传递给发送线程。

<4>发送线程

发送线程被唤醒后在指定地址读入数据,然后按照IEC61850规约中规定的通信帧格式通过以太网将数据发送给二次设备。

当采样线程、数据处理线程或发送线程在运行时如果同步线程收到同步信号1的脉冲,会立刻被唤醒,此时操作系统将暂停其他线程的运行,并将处理器时间片交给同步线程处理同步信号。同步任务结束后,同步线程再次进入等待状态,此时操作系统继续将CPU时间片交给刚才未完成操作的线程继续其处理任务。

图(5)多线程多优先级的任务处理

4.结语

本文提出的使用Windows CE作为合并单元的操作系统相比不使用操作系统或者使用µC/OSⅡ的FPGA+DSP结构的合并单元具有更好的多任务处理能力和更好的系统功能扩展能力,在Windows CE平台下可以更方便的开发基于IEC61850的应用和功能。同时Windows CE也提供对SQL数据库的良好支持,通过ARM9芯片提供的硬盘IDE接口或者SD Card读写接口可以把采样数据实时的保存在硬盘或者扩展卡上做备份。IEC61850是一个面向未来的开放的标准,随着光电流、电压互感器的使用,现代电力技术的发展趋势是将越来越多的间隔层功能下放到过程层中去,使用Windows CE和ARM组合的合并单元可以更方便的进行功能扩展和系统升级。

参考文献

[1] 刘 琨,周有庆,彭红海,等. 电子式互感器合并单元( MU) 的研究与设计[J].电力自动化设计,2006.26(4):67-71

[2] 刘 琨.电子式互感器合并单元( MU) 的研究与设计[D].硕士论文.2006.4

[3]梁晓兵,周捷,杨永标,等.基于IEC61850新型合并单元的研制[J].电力系统自动化. 2007,31(7):85-89

[4]殷志良,刘万顺,杨奇逊,等.一种遵循IEC61850标准的同步的实现新方法[J].电力系统自动化. 2004,28(11):57-61

[5] 田云杰,程良伦,罗晟.基于IEC61850嵌入式合并单元的研究[J].继电器. 2007,35(10):52-55

[6] 窦晓波,吴在军,胡敏强,等. IEC61850 标准下合并单元的信息模型与映射实现[J].电网技术. 2006,30(2)”80-86

[7] IEC 60044-7 Instrument Transformers: Part 7 Electronic voltage transformers. [S]1999

[8] IEC 60044-8 Instrument transformer: Part 8 Electronic current transformers[S]. 2002

[9] 叶宏材,陈峙冉.Windows CE.net 嵌入式工业用控制器及自动控制系统设计[M].清华大学出版社.2005.2

[10]张冬泉,谭南林,王雪梅,等。Windows CE实用开发技术.电子工业出版社[M].2006.4

[11] IEC 61850-7-1 Communication networks and systems in substations: Part1Basic communication structure for substations and feeder equipment - Principles and models[S]. 2001

[12] Douglas Boling. Programming Microsoft Windows CE.NET, Third Edition. Microsoft press, 2003.

[13]殷志良,刘万顺,泰应力,等.一种基于FPGA 技术的电子式互感器接口实现新方法[J].电力系统自动化,2004,28(14):93-99

[14]钱政, 申烛, 罗承沐. 电子式光电组合电流 / 电压互感器中的相位补偿技术[J] . 电力系统自动化, 2002, 26(24) :40- 43

收稿日期:

作者简介:

张晓煜(1984-),男,安徽蚌埠人,硕士研究生,主要从事电力系统自动化的数字化变电站方面研究,(电话)13776633800,(Email)startboy241@tom.com