关键词:PCI总线,WinDriver,直接存储器存取

1 引言

计算机总线扩展技术使得基于计算机的数据采集技术迅速得到应用,基于PC机的数据采集系统是目前应用最为广泛的数据采集系统之一,不但广泛应用于电力设备监控、遥测遥感等测控领域,在声纳、雷达、通讯、地质、医疗器械等领域中也有着重要的应用。高速数据传输始终是计算机相关领域研究的重点,它是计算机感知外部世界并对其进行控制的基础。PCI总线协议是Intel公司1992年提出,为满足高速数据输入/输出要求而设计的一种低成本,高性能的局部总线协议。32位PCI总线的峰值传输速率为132MB/s(33MHz×4Byte)。在PC机的数据传输中,PCI总线以其卓越的性能得到了广泛的应用。高速的数据传输要求提高PCI总线的带宽利用率,使其尽量接近PCI总线的极限速率。本文详细介绍了PCI总线高速数据传输系统设计的关键技术,并实现了一套高速数据采集系统。

2 硬件电路设计

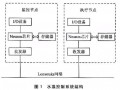

该系统硬件电路板的结构框图如图1所示。其中PCI9054总线控制器负责局部总线与PCI总线间的接口通信。由于PCI9054 Local总线部分信号时序也比较复杂,用门电路不但难以实现而且所需要芯片数量较多,影响电路板的扩充能力及通用性,故采用CPLD实现PCI9054 Local端的控制。从框图中可以看到, PCI9054局部数据总线高五位数据线接到CPLD引脚上,这五根数据线可以接受和发送数据,根据接收到的数据对其译码产生控制信息,还可以发出数据使PCI9054产生门铃中断和MailBox中断。

PCI接口数据传输效率非常高而A/D采集数据效率较低,所以本设计采用FIFO来缓存数据,也可以同时采集多路数据。PCI9054局部总线支持50MHz时钟,为配合A/D工作,本设计选用40M时钟。PCI9054的所有地址线和控制信号都只与CPLD连接,产生CPLD的工作状态和各种控制信息。FIFO采用TI公司生产的SN74V3690芯片,该芯片非常适合于网络,视频,信号处理,电话,数据通信和其他需要大量数据和非对等总线匹配的应用。

图1 硬件电路框图

3 DMA传输方式设计

3.1改进的状态机设计

一般情况下状态机的转换图如图2所示。该状态机有三种传输状态,空闲状态、等待状态和传输状态。该状态机能成功完成与PCI9054的配合数据传输,传输性能稳定,效果较好。是现在PCI9054局部总线状态机设计的一般方法。通过实际测试,在用户模式下,采用该状态机查询方式DM,A传输速率可以稳定达到68M Byte/s.

图2 一般状态转换图

PCI总线峰值速率为132M Byte/s,而以上状态机和传输状态下DMA速率只有68MByte/s说明其中存在不少漏洞。对比该状态机的时序与PCI9054给出的标准DMA传输时序可知,一般状态机在ADS#信号为低后先进入等待状态用来配置各种信号线,然后才开始传输状态。所以每次启动传输都要浪费一个时钟周期的时间,这种浪费在高速数据传输过程中特别是DMA传输中是非常可观的。

而PCI9054标准DMA传输在ADS#信号为低后立刻开始数据传输并不需要等待周期,所以等待周期可以省略,状态机只需要两个状态用来产生时序,即空闲状态和数据传输状态,这样状态机转换过程可以简化。但是由于PCI9054不只需要DMA传输,还需要一些其他操作,比如读写某些控制字和状态标志位等,所以在CPLD中还要区分地址。所以本设计采用了新的状态机,改进的状态机状态转换图如图3所示。

实际测得在同一台机器上,新状态机在用户模式下,查询方式DMA传输速率可以稳定达到88MByte/s。所以在同种情况下,改进的状态机速率可以比原状态机速率高出20MByte/s。由传输速率的大幅提高可以看出,这种改进方式是非常成功的。

图3 改进的状态转换图

3.2 DMA传输模式选择

PCI9054支持两种DMA传输方式:连续模式和集散模式。连续模式即一般的DMA传输方式(块传输),它要求PCI端的物理存储地址连续,Local端地址连续或不变(如从FIFO中读取数据,地址始终不变)。集散模式DMA传输可以申请一个链表式的描述符表用来存储各个物理地址不连续的和传输大小不固定的多块数据的描述寄存器值,PCI9054可以自动通过控制寄存器指针从PCI端或LOCAL端读取寄存器的值并配置寄存器,开始一次次的传输。通过集散模式DMA传输,可以一次传递更多的数据。但是集散模式DMA传输在传输完一块数据之后要重新配置寄存器的值,所以速度比连续模式稍慢。

本设计对两种DMA传输模式进行了对比,在其他条件相同的情况下,通过逻辑分析仪测得连续模式下DMA传输速率为95.3M Byte/s,集散模式下DMA传输速率为91.2M Byte/s。 可以看出,连续模式在同种情况下速度要比集散模式高出4M Byte/s。但是连续模式由于只能单次启动DMA,所以传输数据量大小有限,这在大量的数据传输是非常不利。而集散模式由于可以在传输过程中通过描述符表重新配置寄存器,所以可以一次传输较大的数据量,且重新配置寄存器的工作不需要驱动程序干预,PCI9054会自动完成该过程,所以可以在传输速度降低不多的情况下得到更大的数据量。集散模式传输是PCI9054支持的DMA传输的特色模式。实际测得,在赛扬1GHz,256M内存机器上,相同条件下,连续模式最多可以一次传输4MByte数据,而集散模式最多可以一次传输32MByte。集散模式可以传输的数据量远远大于连续模式。所以在需要一次传输的数据量较大而速度要求相对不太严格情况下集散模式是较为理想的选择。

3.3 终止方式选择

DMA过程的终止可以通过查询和中断两种方式检测到。查询方式DMA传输原理为在启动DMA之后一直读取寄存器DMACSR0[4]的值,当该位为1时表示DMA传输完毕。中断方式DMA为在启动DMA时使能DMA完成中断,系统接收到中断之后在中断处理例程中讲清空中断,并读取DMA传来的数据。

在相同条件下测得查询方式下连续DMA传输速率为95MByte/s.中断方式下连续DMA传输速率为114.2MByte/s。

由两种终止方式速度比较可知中断方式在同样条件下能比查询方式速度提高将近20MByte/s 。PCI总线极限速度为132MByte/s,而这种传输方式速率已经达到114MByte/s,所以这种方式DMA速度已接近PCI总线的峰值速度。

4 驱动程序设计

4.1驱动程序的引出

从最广泛的意义讲,一个“驱动程序”是操作一个硬件设备的一组函数。在任何操作系统上,设备驱动程序都必须与基本的系统代码进行和谐的作用。Microsoft为保证系统的安全性、稳定性、可移植性,对应用程序访问硬件资源进行了限制,不能直接进行物理内存、I/O端口的访问以及中断处理等硬件操作。

4.2 使用WinDriver开发设备驱动程序

1)驱动程序开发环境选择

开发设备驱动程序的软件平台有很多种,如DDK、VTOOSD、WinDriver、DriverStudio等.本设计采用WinDriver来开发设备驱动程序.WinDriver对常见的PCI接口芯片(AMCC、PLX系列)提供了很好的支持,有专门的函数供开发人员利用,方便了驱动程序的开发.

2)本设计用户模态下的驱动程序介绍

WinDriver驱动程序可以分为两种工作模式,即用户模式和内核模式。本设计用户模式下的驱动程序的功能包括:PCI配置寄存器访问、映射到局部空间的各种寄存器访问(包括局部控制寄存器、RunTime寄存器、DMA寄存器、和消息队列寄存器),各种PCI设备选择,EEPROM访问,IO操作,LOCAL映射的各个空间的访问,DMA操作,中断处理等。

3)本设计中内核驱动程序的设计

数据采集需要传送大量的数据,需要快速的将采集到的数据传递给主机,数据传送占用时间越短,应用程序能利用的时间也就越多,从而对于数据采集卡和主机之间的相互通信和数据传输提出了较高的要求。编写该设备驱动程序的关键性问题在于:快速可靠的DMA传输、响应及时的中断处理等。WinDriver提供了Kernel PlugIn技术,能够实现理想的中断响应速度,解决对于高性能的需求。为了提高系统的整体性能,在用户模式下驱动程序的基础上采用了Kernel PlugIn技术。将中断,DMA处理转移到内核模式下执行。从而大大提高了系统的处理速度。

4)DMA速率探讨

系统数据传输不仅需要传递数据,还要通过中断来引发数据传输和传输结束呼叫。

传输时间 = 中断时间 + DMA传输时间

通过逻辑分析仪查看硬件波形图可以计算出内核模式下中断触发DMA传输速率为105.4MByte/s。所以数据持续传输速率可达105MByte/s。可以看到,中断响应时间也影响数据传输的最终速度。

由第四章DMA部分讨论可知,用户模式下测得的DMA传输期间最快速度为95MB/s。内核模式下DMA速度最快为114MB/s。而最初的DMA传输速度为68MB/s。从最初到现在,DMA传输期间传输速度提高了46MB/s。

结束语

在现代信号处理技术中,通过PCI总线进行快速数据传输是实现主机与外设间通信的主要方式。作者在实验室利用PCI9054接口芯片设计了一个带有12通道的高速信号采集器。对影响数据传输速率的各个环节逐一考虑,提出了一整套数据传输方案。将数据持续传输速率提高到100MByte/s以上。接近PCI总线的极限速率。

本文的创新点是:对局部总线状态机状态转换进行了研究。局部总线状态机采用改进的状态转换逻辑,将DMA数据传输效率提高了约20MByte/s。

参考文献:

[1]裴喜龙,童莉.基于PCI总线的高速数据采集卡系统设计与实现[J].微机算计信息,2006,7-1:129-131。

[2]WinDriver v6.23 User’s Guide[DB/OL].http://www.jungo.com.2004。

[3]PCI9054 Data Book[DB/OL].http://www.plxtech.com.2000-01。

[4] 李贵山,陈金鹏主编.PCI局部总线及其应用.西安:西安电子科技大学出版社[M].2003。

[5] 侯伯亨,顾新著.VHDL硬件描述语言与数字逻辑电路设计.西安:西安电子科技大学出版社[M].1997。

[6] 乔林,杨志刚著.Visual C++高级编程技术DirectX篇.北京:中国铁道出版社[M].1998。

[7] 胡波,原新晶.WinDriver 开发驱动程序的KernelPlugIn技术的研究与应用[J].计算机应用,2003,23(11)。