关键词:PC/104总线、CAN总线、CPLD、多串行口

Abstract: Design and realization of a communication module with 4 serial ports and a CAN bus interface is presented in this paper. It is based on PC/104 standard. All control logics in the module are occurred by a CPLD device. Time sequence between 104 bus and CAN controller is also adjusted by CPLD.

Key words: PC/104 bus , CAN bus , CPLD, Multi serial ports

1 引言

PC/104总线计算机具有体积小、功耗低、工作温度宽、可靠性高等特点,被广泛地应用于分布式系统和集散控制系统中作为现场控制计算机。在这些系统中的104PC,往往需要同上位机及下面连接的控制执行机构、传感器或测量仪表通信,而常用的通信方式有RS-232串行口加MODEM方式、RS-485方式、以太网方式以及各种工业现场总线。

RS-232串行口加MODEM方式一般用于点对点之间较远距离的数据传输;RS-485方式一般用于控制现场对多点实施控制,目前它仍是工业控制中使用得最广泛的一种方式;以太网方式可以实现远程控制和信息共享,但它的时延不可控,在实时性和保密性要求较高的控制系统中的应用受到一定限制;现场总线技术是当今自动化领域技术发展的热点之一,是应用于控制现场、在微机化测量设备之间实现双向串行多节点数字通信的系统,也被称为开放式、数字化、多点通信的底层控制网络。现场总线的标准很多,其中CAN总线在国内的发展速度最快,被认为是替代RS-485的最理想的方式之一。

CAN总线规范已被ISO制定为国际标准,其模型结构有三层,包括OSI底层的物理层、数据链路层和顶层的应用层,通信速率最高可达1Mbps/40m,直接传输距离最高可达10Km/5Kbps,可挂接设备数最高可达110个。总线的电气规范类似于RS-485,采用双线差分平衡传输,以两线间的电压差表示数字逻辑,分为“显性”和“隐性”两种逻辑。CAN总线采用面向内容的编址方案,可以在总线中加进一些新站而无需在硬件或软件上进行修改。该总线以报文为单位进行数据传送,报文的优先级结合在11位标识符中,确保不同实时性要求的数据以不同优先级传送,总线读取中的冲突可通过位仲裁解决。CAN协议可使用五种检查错误的方法,保证了数据传输的可靠性。利用CAN总线可以以较低的成本、较高的实时处理能力和在恶劣的强电磁干扰环境下可靠地工作。

综上所述,根据目前104PC在工业控制中的应用特点和需求,本设计的目的是按照PC/104标准设计通用型多功能扩展通信模块,该通信模块包括两个RS-232串行口、两个RS-485接口和一个CAN总线接口。

2 器件选型和总体设计方案

要按照PC/104标准在通信模块中扩展四个串行口和一个CAN总线接口,在模块功耗和外型尺寸上限制很严,因而器件需选择高集成度IC。

异步通讯单元是串行口扩展的核心器件,它在指定波特率和数据格式下完成并行数据和串行数据之间的相互转换并完成相应的控制。设计中选用了TI公司的高集成度异步通讯控制单元TL16C554芯片,它集成有4个ACE(异步通信单元),共用了数据线和一些逻辑控制信号,可以通过各自的片选信号选择每一个ACE单元。每个收发单元都有自己的中断请求、数据收发以及MODEM逻辑控制信号,可以完成异步收发器的所有功能。

RS-232C电平与TTL电平转换通过Max213完成。Max213采用的是SSOP封装,外型尺寸小,功耗小,一片Max213加上几个小电容就可以完成一个标准RS-232C所有信号的电平转换。

RS-485电平与TTL电平转换通过SN65LBC184实现。SN65LBC184是德州仪器公司推出的RS-485总线驱动芯片,结构简单,功耗小,由单芯片实现半双工RS-485通信。它采用1/2负载设计,总线上允许挂接64个单元,还具有防静电、耐高压冲击和过热保护功能,可以提高系统的可靠性。

CAN总线控制器是实现CAN总线接口扩展的核心器件。它将来自104PC上ISA总线的并行数据按照CAN总线协议转发出去,同时也按照CAN总线协议接收来自外部总线的数据。在设计中选用了PHILIPS公司的SJA1000独立CAN总线控制器。SJA1000是PCA82C200的升级产品,集成了CAN总线逻辑链路层协议。它与PCA82C200在硬件和软件上完全兼容,还具有支持扩展CAN总线协议的PELI工作模式(支持CAN2.0B协议)。具体来说,SJA1000主要具有以下特点:扩展的64 Byte FIFO接收缓冲、支持11bit标识码和29bit标识码、支持标准和扩展格式的帧信息的传输,还具有单/双掩码滤波器、仲裁丢失中断、只听模式、自身信息接收、最近错误寄存等众多PELICAN模式扩展功能。

CAN总线电平与TTL电平的转换通过PHILIPS公司的PCA82C250完成。该芯片与ISO11898标准兼容,支持最高达1Mbaud的高速传输,可连接110个节点。采用限斜率控制,降低射频干扰,具有宽范围的抗共模干扰、抗电磁干扰能力。

设计中所涉及到的逻辑控制、时序控制由CPLD实现。这样做的目的,主要出于以下考虑:

·如果采用与非门,译码器、锁存器等分立元件实现逻辑控制,大量的元件难以在PCB板上布局,而且使电路变得复杂,也降低了模块的可靠性和抗干扰能力。

·CAN控制器SJA1000的对外操作接口是一种地址/数据分时复用的接口,而PC104没有地址/数据分时输出的特性。因此,必须经过时序转换才能实现它们之间的连接。目前,一般采用8031单片机转发数据的方式来实现:通过8031连接CAN控制器,104PC利用IO端口读写的方式将数据直接传送给8031,或者将数据写于双口RAM中,8031在另一个口读取数据,再由它对CAN总线控制器进行操作,将数据转发出去。这种方法无疑又要增加器件和电路的复杂性。

为此,设计了通过CPLD整合时序实现104PC与CAN控制器连接的方法,由104PC分时送出操作地址和操作数据,并由CPLD整合相关的逻辑控制信号,满足CAN控制器的时序要求。

·采用CPLD可以根据需要定义输入输出脚,方便PCB板布局和走线。

·采用CPLD时不必担心设计中所采用器件的种类、数量,可以任意定义所需各种器件,从而优化电路性能。

·采用CPLD可以通过软件对电路进行仿真,方便电路调试。

·采用CPLD可以在线修改其内部逻辑,升级或修改BUG时可不改动外部电路。

CPLD芯片选用ALTERA公司的EPM7064SLC84-10,该芯片具有基于EEPROM的第二代MAX结构,支持通过JTAG引脚实现在系统编程。拥有64个宏单元,4个逻辑阵列块,1250个可用门单元,支持5V/3.3V多电压IO接口,可提供68个用户IO引脚。

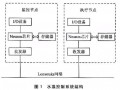

根据以上的方案,通信扩展模块的结构如图1。

图1 扩展通信模块结构

3 硬件实现

3.1地址译码电路

本扩展模块共需占用七个IO地址,其中两个IO地址供CAN控制器,四个IO地址供四串口异步通讯单元,一个IO地址供中断共享电路。必须合理选择IO地址,否则会引起系统不可预知的冲突。

各种PC104计算机IO地址分配情况大体相同,以盛博SysCenterMoudle/SuperDx为例,选择了110H~140H为扩展通讯模块的IO地址,地址分配见表1,逻辑译码结构见图2。

表1 IO地址分配表

图2 IO地址逻辑译码结构

图2用VHDL语言可以很方便地实现。其具体描述如下:

SEL(0)<=AEN;

SEL(1)<=NIOW AND NIOR;

SEL(2)<=ADDR(0);

SEL(3)<=ADDR(1);

SEL(4)<=ADDR(2);

SEL(5)<=ADDR(3);

SEL(6)<=ADDR(4);

SEL(7)<=ADDR(5);

SEL(8)<=ADDR(6);

WITH SEL SELECT

Y<="1111110" WHEN "010001000",//IO/110 地址操作

"1111101" WHEN "010001100",//IO/118 数据操作

"1111011" WHEN "010010000",//IO/120 串口1

"1110111" WHEN "010010100",//IO/128 串口2

"1101111" WHEN "010011000",//IO/130 串口3

"1011111" WHEN "010011100",//IO/138 串口4

"0111111" WHEN "010100000",//IO/140 读中断号

"1111111" WHEN OTHERS;

END BLOCK CODE;

3.2 104总线与CAN控制器的接口

如前所述,104总线与ISA总线兼容而与CAN控制器要求的时序不同,设计中将104总线中的BALE、地址和读写信号经CPLD逻辑整合后提供给CAN控制器,同时从数据线分时送出操作地址和操作数,满足CAN控制器的时序要求。时序整合的VHDL语言如下:

ALE<=(NOT Y(0)) AND BALE;

CSCAN<=Y(1);

IORCAN<=Y(1) OR NIOR;

IOWCAN<=Y(1) OR NIOW;

双向数据缓冲的VHDL实现可以在很多参考书中找到,此处从略。

3.3 异步通信接口电路及中断共享电路

16554的接口可与PC104实现无缝连接,CPLD实现选通和读写逻辑控制,异步通信与CAN控制器共用CPLD内的双向数据缓冲电路。

异步通讯控制单元16554有很强的中断能力,四个串行控制器具有各自的中断引脚,使用灵活。但系统的中断资源有限,如果每一个控制器都占用一个中断号,通讯模块需要占用五个中断号。为了节约中断资源,设计中将4个串口控制器共享一个中断,而CAN总线控制器单独占用一个中断。

为了实现共享,设置了一个中断向量寄存器,当发生中断时首先读取中断向量寄存器以定位发出中断的串行口。其原理见图3。

图3 中断共享电路

VHDL语言实现如下:

GMID<=NIOR OR Y(6);

INTSER<=INTABCD(0) OR INTABCD(1) OR INTABCD(2) OR INTABCD(3);

INTID<=INTABCD WHEN (GMID=‘0‘)

ELSE

"ZZZZ"

4 结论

本设计利用CPLD实现了104总线和CAN控制器之间的时序转换、整个电路的逻辑控制以及中断共享,使电路设计结构紧凑,性能稳定。扩展了RS-232、RS-485和CAN接口的104PC可以满足绝大部分控制系统的通信要求。该设计已被一个分布式防空系统所采用,在历次联调试验中性能指标均达到了要求。

参考文献

1. 盛博科技有限公司.PC/104 技术手册.SBS Science&technology Co,2000

2. Altera. MAX 7000 Programmable Logic Device Family Data Sheet.1995

3.Texas Instruments. TL16C554 Asynchronous Communication Element Data Sheet. 1998

4. Philips Semiconductors. SJA1000 Stand-alone CAN Controller data sheet. 1997