摘要:叙述嵌入式计算系统在开发阶段、生产环境和现场环境三种情况下的调测技术

和方法,以及如何在硬件和软件设计中进行可观测性和可测试性设计。

关键词:在线测试 可观测性 可测试性 BDM JTAG

引言

对于含有微处理器的装置来说,调测总是软件和硬件结合的。在产品开发的阶段以排错为

主,在产品开发后期以及生产和现场运行阶段,则是以测试为主。不同的阶段,调测的内

容、手段和使用的工具不尽相同。

测试接口并不是系统功能的一部分,测试接口设计本身也需要成本。对于小型简单系统来

说,没有必要也不允许(成本考虑)设计测试接口;对于复杂系统来说,设计测试接口的

花费是值得的。良好的测试接口设计可经缩短产品的开发周期,给产品维护、维修带来便

利。

对于嵌入式计算系统来说,测试往往是软件和硬件相结合的,既有借助于“正确”的软件

来测试硬件,也有借助于“正确”的硬件来测试软件。由于软件设计人员和硬件设计人员

的技术隔膜,二者常常在出现问题后相互指责,难以界定是软件还是硬件问题。对于嵌入

式系统的软件设计人员

来说,必须对硬件有足够的了解。这一点,和通用计算平台上的软件设计是不同的;反之

,硬件人员也必须能够编写一些测试软件,以证明其设计的正确性。

1 开发阶段的调制方法

1.1 RAM版本的目标系统调试

通过ICE(In-Circuit-Emulate)来调试目标板是开发人员最常用的手段。在产品开发初

期,由于各种软件和硬件问题很多,通过仿真器并结合逻辑分析仪、示波器等硬件信号测

试工具能够很好地发现问题。

在仿真器环境下,通过仿真器的监控软件来控制用户软件的运行,使用断点、单步跟踪和

查看变量、CPU寄存器、存储器的数值等手段来查找问题。由于仿真器的软件和硬件需要

一定的CPU资源,用户软件在仿真器环境下运行和脱离仿真器后独立运行是有区别的。好

的仿真器能够尽量减小这

种区别。常见的仿真器从技术上区分有:单CPU仿真器、双CPU仿真器和ROM仿真器。

在仿真器环境下,程序一般是在仿真器的RAM存储器中运行的,所以这种阶段也称为“RA

M版本的目标系统调试”。

1.2 ROM版本的目标系统调试

在仿真器环境下,目标板运行调试正确后,一般的做法是将应用程序写入目标板的非易失

性存储器中,让目标板单独运行。在很多情况下,目标板系统往往不能运行或者运行结果

和仿真器环境下不一致。而没有连接仿真器,无法观察各种软件状态,给分析问题造成一

定困难。在目标板上设

计指示电路有助于发现问题;在电路板上增加1个LED是最简单也是很有效的方法。对于复

杂系统,可以设计1个数码管显示输出接口,或者设计1个调试用串口,将调试信息发送到

PC机上显示。

在使用PC机作为显示输出设备时,一般的做法是使用Winodws自带的超级终端软件,无需

另外编制程序。和前二种方法相比,该方法的接口信号是双向的,调试者可以通过PC机输

入信息到目标板中,设定显示信息的类别。这一点,对于复杂系统的调试是很有价值的,

CISCO公司的很多路由器

产品就使用这种方法来维护和调试。

2 生产阶段的测试方法

生产阶段的测试只是对硬件电路或者系统进行测试。测试目的是为了对产品或者部件进行

分检,找出有缺陷的产品。测试内容包括:

*裸板测试——检查未安装元器件的电路板上的开路和短路缺陷;

*成品生产缺陷分析——检查已安装元器件的电路板上焊点的短路和开路缺陷;

*成品电气性能测试——认证每个单元器件的上电运作;

*产品功能测试——认证电路模块的功能。

生产测试和开发阶段的硬件测试不同,需要测试方法快速、能成批测试,易于在制造生产

线上安装。在生产的不同阶段使用的测试工具和技术也不相同。目前常用的测试工具和技

术有:人工视觉检查(MVI)、在线测试(ICT)、自动光学测试(AOI)、自动X射线测试

(AXI)。其中人工视

醪馐裕∕VI)只能用于小批量试制产品。

在线测试(ICT)是最常用的一种线路板测试方法:使用专门的针床与已焊接好的线路板

上的元器件接触,通过针床在线路板上施加微小电压来测试线路通断、元件是否正确安装

。由于需要为特定电路板设计专用夹具,适合于单一品种民用型家电线路板极大规模生产

的测试;缺点是在高密

鹊腟MT线路板测试困难。目前的替代解决办法是使用光学方法测试(如AOI,AXI),或者

使用边界扫描技术(即基于IEEE1394标准的JTAG测试接口)测试。后者需要IC或者线路板

支持此技术。

功能测试是生产过程的最后阶段使用,测试线路板或者系统的功能指标,一般的功能测试

需要设计专用测试设备和测试软件。

3 现场测试技术

现场测试分为三种情况:一种是在线测试,测试设备不停止运行;一种是停机测试,被测

试设备停止运行;第三种为脱机测试,将被测部件从运行现场取出,放到专用的测试装备

上进行测试。从测试技术角度上说,后二者更容易进行各种测试;对于复杂系统来说,往

往故障和问题需要在设

备运行时才能发现和定位,必须进行在线测试。究竟采取哪种方式进行现场测试,取决于

故障状况和实际应用是否允许立即停机。

开发阶段产品和成熟产品的现场测试要求也不同:前者测试目的主要是发现设计中的问题

,由产品开发人员进行;后者侧重于发现使用中的问题和失效的部件,目的是更换部件,

由产品使用人员进行。(但测试方法和步骤也有可能是设计人员制定的。)

现场测试和试验室测试的最大区别就是测试设备难以安装和连接:线路板封闭在机箱中,

测试信号线很难引入,即使设备外壳上留有测试插座,测试信号线也需要很长,传统的在

线仿真器在现场测试中无法使用。另一方面,现场往往没有实验室里的各种测试仪器和设

备,因此,必须有更好

的方法和手段来完成测试。

嵌入式处理器中目前有很多芯片具有类似Motorola公司683XX系列处理器的BDM调试接

口(详见第5部分)。这种接口是串行的,处理器内部固化了调试微码,为现场测试

带来了方便。对于不具备这种接口的嵌入式计算系统,在系统设计时将关键信号点引出到

一个测试接口插座上,通过该插座可输入测试激励信号和观察输出信号;对于软件测试,

可使用前文中所述的ROM板测试方法,外接显示部件来观察程序运行情况。

软件现场调试的另外一个要求是程序应能够现场下载,以便在发现问题后能够修改软件。

现场在线下载程序的方法有两种:一种是使用具有ISP功能的处理(如Philips公司的P89

C51RD系列MCU等),另一种方案是将软件设计成两部分,一部分是应用功能软件,另一部

分是完成前者下载到系

持械南略赝ㄐ湃砑?N蘼勰闹址椒ǎ?略氐闹骰??荘C机。如果需要达到远程调试和下

载的目的,则要使用后一种方案。例如,在Echelon公司的Lonwork现场总线产品中,每个

节点中的程序均可以通过网络下载,这种功能为多节点网络系统的现场调试带来了极大方

便。

4 可测试性设计

在产品开发初期,产品测试的目的是验证产品设计的正确性,而可测试性部件的存在则能

加快测试速度,缩短产品开发周期;在生产阶段,通过测试来剔除有缺陷的产品和部件;

在使用阶段,测试则用于故障定位,找出失效的部件并更换或者维修。可见,产品的测试

在产品生命周期各阶段

均有十分重要的作用。可测试性设计应该在产品设计初期就加以考虑,结合测试在不同阶

段的作用来设计测试模块和接口。

产品的可测试性设计要考虑的问题有:测试的目的、测试部件的位置、测试部件的基本要

素、内置测试部件与外部测试设备仪器之间的电气和机械连接,添加测试部件对被测模块

功能和性能的影响、测试部件的成本以及何时使用测试功能等。

如前所述,测试在产品不同阶段是有差别的。在产品开发阶段,很多参数需要定量和详细

地进行测试,以验证产品在各种不同情况下是否能正常工作;测试参数,测试点较多,可

以方便地连接各种外部测试仪器,也不需要考虑添加测试部件所带来的附加成本。在产品

生产和使用阶段,测试

的节点和参数数量也相对减少,测试一般是定性的,无需借助于外部设备的自测试,成本

因素也必须考虑。

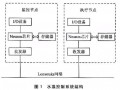

测试部件一般位于被测部件的接口和边界位置上,如图上所示,用于产品控制被测部件的

激励信号和采样被测部件的输出信号。测试部件一般由测试信号源、信号传输通道、测试

观察装置等组成。测试部件可以完全包含在被测部件中,也可部分位于外部(如外接信号

源和示波器等)。对于

自动测试,测试部件还包括被测部件的预期输出存储部件比较部分。

在一个系统中,如何划分模块,确定测试位置(即模块的边界)是关系到可测试性设计是

否合理的首要问题。模块间最小相关原则和模块内最小相似原则是两个重要依据:前者保

证测试可以独立进行,不需要很多其它模块的配合;后者可以使测试能正确反映被测模块

的大部分工况,不至于

漏测很多工作状态。

很多情况下,从被测模块的边界直接引出信号有困难,测试信号需要经过其它模块引入到

被测模块上。如果作为信号路径的模块对信号特征没有改变,则称这种测试路径是透明的

,路径模块必须能在旁路模式和正常工作模式之间切换,实现起来有局限性。对于硬件来

说,最简单的透明路径

是使用跳线。

对于简单嵌入式系统来说,测试一般包括上电自测试和人为测试。后者在故障出现时进行

。对于复杂系统来说,还包括定时自动测试,比如在大型程控交换机和飞机机载电子设备

的运行过程中,均定时进行自检。

可测试性设计还应考虑测试功能所使用对象的不同。产品设计人员、产品使用人员和产品

维护人员对测试内容的要求是同的,需要进行分层次的可测试性设计。

对于硬件和系统的可测试性设计已有IEEE1149.1/4/5等标准可以借鉴,对于单纯的软件测

试,目前尚无具体和统一的标准,只有诸如代码格式分析、白盒测试、黑盒测试、覆盖测

试等测试方法。软件测试的途径有两个。一是在源代码中增加大量测试代码,使用条件编

译指令来控制形成调试

、测试和最终发布等不同版本。调测版本的代码规模要比最终的发布版本大很多,在问题

解决后,一般将临时性测试代码通过编译开关屏蔽。另外一个软件测试途径是使用专用的

测试软件(如法国Telelogic公司的LOGISCOPE测试工具),这些测试软件能完成诸如覆盖

测试、代码格式分析等

功能,但均是针对特定的语言和操作系统环境,使用上一些限制。

还需要说明的就是“可观测”设计的概念。可观测性和可测试性不同,不需要加入激励信

号,只观察系统运行中某些内部状态,比如软件中某个重要变量的数值变化,硬件电路中

某个IC引脚的信号电平等。在设计中,应该保留这些观察接口,以便需要时用它来判断和

分析系统的问题。一个

可测试的系统,一定是可观测的,反之则不然。设计可测试性系统的目的是为了以后修改

和改进设计,而使系统具有可观测性则是为了维护系统,判断哪个是出故障的部件,以便

更换。可测试性设计一般用于新产品,而可观测性设计用于成熟产品。当然,在结构、安

装条件和成本允许的情

况下,成熟产品也应具有可测试性。实际上,由于处理器技术和芯片的日新月异,已经不

存在真正意义上的成熟产品了。

在一类产品中的可测试性设计应该具有一致性,例如,用红色LED表示电源状态,所有电

路板均应采用红色LED,点亮的频率也应该一致。作为企业,应制定相关的测试接口标准

,并且这些标准应符合行业习惯或者行业标准。

5 测试和调试接口标准

测试和调试接口标准:JTAG和BDM。

5.1 背景调试模式

在使用传统的ICE来调试时,使用ICE中的CPU来取代目标板中的CPU,目标板和ICE之间使

用多芯扁平电缆来连接,而ICE在使用时一般还需要缩主机(一般来PC)来连接。

在一些高端微处理器内部已经包含了用于调试的微码,调试时仿真器软件和目标板上的C

PU的调试微码通信,目标板

上的CPU无需取出。由于软件调试指令无需经过一段扁平电缆来控制目标板,避免了高频

操作限制、交流和直流的不匹配以及调试线缆的电阻影响等问题。这种调试模式在Motor

ola公司产品68300系列中被称为背景调试模式BDM(Background Debug

Mode)。在仿真器和目标之间使用8芯(或者10芯)的BDM接口来连接,其他公司的嵌入式

处理器也有类似功能,不过叫法不同,例如AMD公司在其X86微处理器上提供“AMDebug”

的调试接口。

实际上,BDM相当于将ICE仿真器软件和硬件内置在处理器,这使得我们直接使用PC机的并

口来调试软件,不再需要ICE硬件,大大节约了汽油发成本。一些调试器供应商也提供这

种软件产品(如XRAY)。对于用户来说,为了调试一些特定问题,可以直接使用BDM命令

来调试目标系统,以弥补

商业调试软件的不足。

BDM接口有8根信号线,也有为10根信号线的,如图2所示。调试软件通过4脚使CPU进入背

景调试模式,调试命令的串行信号则8通过脚输入,同时4脚输入信号步时钟,而CPU中的微

码在执行命令后会在10脚输出调试结果指示信号。可见,BDM接口引线由并口和PC机相连

,调试命令则是通过串行

方式输入的。

目前在CPU内置的调试接口和微码方面,各厂家尚无统一标准。处理器厂家、工具开发公

司和仪器制造商曾于1998年组成了Nexus 5001 Forum(Nexus 5001论坛),成员包括Motor

ola、Infineon

Technologies、日立、ETAS和惠普公司等,正致力于制定一个统一的片上通用调试接口。

这方面的进一步情况可查阅http://www.nexus-standard.org/网站。

5.2 边界扫描测试技术和JTAG接口

边界扫描测试技术(Boundary-Scan Test Architecture)属于一种可测试性设计。其基本思想是在芯片引脚和芯片内部逻辑之间(即芯片边界位置)增加串行连接的边界扫描测试单元,实现对芯片引脚状态的设定和读取 ,使芯片引脚状态具有可控性和可观测性。

边界扫描测试技术最初由各大半导体公司(Philips、IBM、Intel等)成立的联全测试行

动小组JTAG(Join Test Action Group)于1988年提出,1990年被IEEE规定为电子产品可测试性设计的标准(IEEE1149.1/2/3)。目前,该标准已被一些大规模集成电路所采用(如DSP、CPU、FPGA等),而访问 边界扫描测试电路的接口信号定义标准被称为JTAG接口,很多嵌入式处理器内置了这种测 试接口。在Cygnal公司腃8051F000系列单片机中和一些FPGA芯片中,JTAG接口不仅能用于测试,也是器件的编程

接口。

IEEE1149.1标准支持以下3种测试功能:

*内部测试——IC内部的逻辑测试;

*外部测试——IC间相互连接的测试;

*取样测试——IC正常运行时的数据取样测试。

图3给出了具有2个芯片的系统的边界扫描测试原理。

图3中,TCK为测试同步时钟输入,TMS为测试模式选中输入,TDI为测试数据输入,TDO为

测试数据输出,由测试移位寄存器产品。图3中的小方框表示位于芯片外围的边界扫描测

试逻辑单元,芯片每个引脚信号经过边界扫描单元和内部的功能单元相连接。

目前,边界扫描技术的应用主要在数字IC的测试上,这种设计思想也可用于模拟系统、板

级测试甚至系统测试上。IEEE也制定了和IEEE1149.1相类似的标准IEEE P1149.4(数模混

合信号测试总线标准)、IEEE 1149.5(电路板测试和维护总线标准)。